专为物联网打造的开源处理器PULPino

苏黎世联邦理工学院(ETH Zurich)与意大利波隆纳大学(University of Bologna)的研究人员共同开发出1款开放源码的处理器PULPino,专为低功耗的可穿着装备与物联网(IoT)利用优化。

开放源码和协同开发是现今软件世界的标准作法,例如Linux。虽然也有1些像OpenRISC与Opencores等硬件计划,开放源码的硬件在板级开发时更能获得较大动能。例如Arduino与Raspberry Pi的PCB设计可公然获得。但是,这些开发板上所采取的芯片依然是专有的。

如今,这支由ETH Zurich教授Luca Benini带领的研究团队已将其微处理器系统的1项完全设计公然在公共领域了,这就是PULP计划(平行超低功耗)的衍生系统。

32位的PULPino是专为以电池供电的超低功耗装置而设计,其算术指令也是开放源码的:研究人员们打造的这款处理器可兼容于加州大学伯克利分校(UC Berkeley)所开发的RISC-V开放源码指令集。

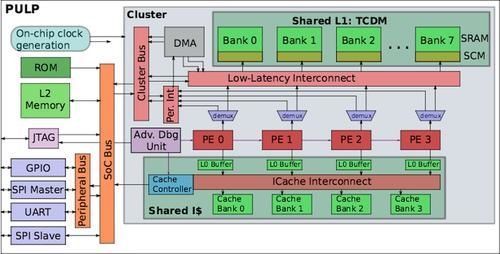

PULP采取4 核心的处理器设计

Source:ETH Zurich

PULPino是更通用的PULP之简化版,内建单1处理元素以取代4处理元素猬集,而且也简化了指令与数据RAM,并于2015年时采取FPGA建置。根据官网的简报数据,PULPino核心称为RI5CY,是1种RISC-V的4阶循序管线建置。

研究人员开发的处理器核心可媲美ARM Cortex-M4核心,具有趋近于1 的每周期数指令集,支持基础整数指令集(RV32I)、紧缩指令集(RV32C)和部分支持乘法指令集扩大(RV32M)。它为硬件回路建置了非标准扩 展、后递增加载与贮存指令集、ALU与MAC作业。为了履行FreeRTOS等嵌入式操作系统,并支持特权规格子集。当核心闲置时,该平台可切换至低功耗 模式,在出现事件/中断时仅启动单1事件单元并唤醒核心作业。

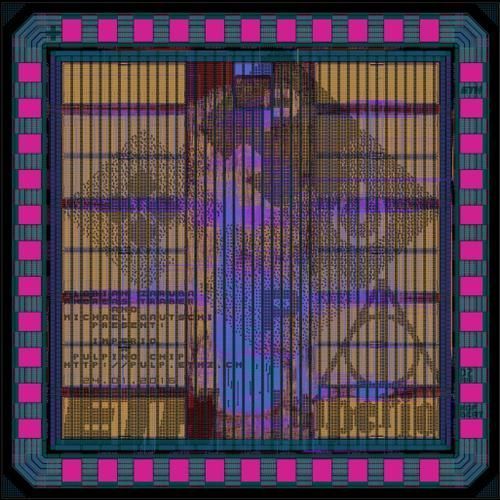

PULP4核心IC采取Globalfoundries的 28nm制程,已于2015年11月投片;首批ULPino核心设计则在2016年1月采取联电(UMC)的65nm CMOS制程投片。PULPino平台可用于RTL摹拟,实现FPGA与SoC。具有完全的除错支持,包括FreeRTOS;作业于400MHz频率频率 与1.2V的电压,芯片功耗约32.8mW。

PULPino (Imperio)芯片图

Source:ETH Zurich

根据研究人员表示,使用PULPino的授权将会“10分宽松”,而且也与正开发中的另外一开放源码处理器lowRISC1致。

“从最近许多开放源码硬件的例子来看,使用权常常遭到独家销售权与非竞争条款的限制,”Benini说,“但我们开发的系统并未针对授权附加任何限制条件。”

研究人员预计,PULPino可以用来驱动智能手表、监测生理功能的传感器或物联网传感器。 PULPino目前已用于瑞士与欧洲研究机构的其他研究计划,和英国剑桥大学(Cambridge University)。

Benini认为,欧洲的中小企业(SME)应当也会对PULPino感兴趣,由于他们常常没法负担开发ASIC的本钱。透过开放来源的免授权费设计,可望大幅下降开发本钱,从而使SME与ETH沾恩。

-

张艺谋妻女晒自拍母女颜值爆表

明星,怎么说也是个人吧。时不时晒晒照片,来个自拍什么的不足为奇。明星张婷与其女儿,在平安夜当晚晒自拍...[详细]

-

视帝陈豪爱妻陈茵媺爬山遇发哥为拍贴脸合照

视帝陈豪的爱妻陈茵媺“野生捕获”到周润发,抛开丈夫,完全放下矜持,就像树熊那样缠绕树干般搂紧周润发脖...[详细]

-

蒙面唱将猜猜猜第三季播出时间

《蒙面唱将猜猜猜》第三季于2018年10月21号每周日晚21:10分播出。《蒙面唱将猜猜猜》是江苏卫视的王牌节目,201...[详细]

-

郑爽才是中国好老板让助理出演角色进军娱乐

在年初的时候说到 中国好老板 ,大家的第一直觉就是我们的大幂幂了,用一部《三生三世十里桃花》把旗下的艺人...[详细]

-

盘点娱乐圈当下最俊朗的五大男神你喜欢哪一

靳东,1976年12月22日出生于山东,中国内地男演员。1993年,在电视剧《东方商人》中饰演少年高显扬;2005年,出演...[详细]

-

-

默沙东HIF-2α抑制剂维利瑞®(贝组替凡)在华获批

上海2024年11月21日 /美通社/ --默沙东(默沙东是

-

天港医诺完成数千万元人民币pre-A+轮融资,加速推进创新免疫药物临床转化

合肥2024年11月22日 /美通社/ -- 近期,合肥天港

-

"2024年度首届科利耳®Graeme Clark格雷姆•克拉克奖学金"正式颁发

传承大爱之声,共筑非凡未来 北京2024年11月2

-

逐"绿"前行 "美丽"升级 重庆着力建设美丽中国先行区

重庆2024年11月22日 /美通社/ -- 以下为来自iChong

-

恩凯赛药完成数千万元A++轮融资,加速推进NK细胞免疫产品管线

上海2024年11月22日 /美通社/ -- 近期,恩凯赛药

-

诺华荣登2024年药品可及性指数排名榜首

该指数彰显了诺华在药物研发与药品可及性方

-

-

-

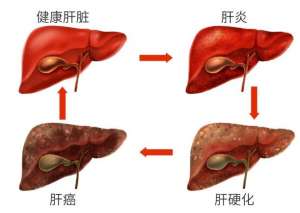

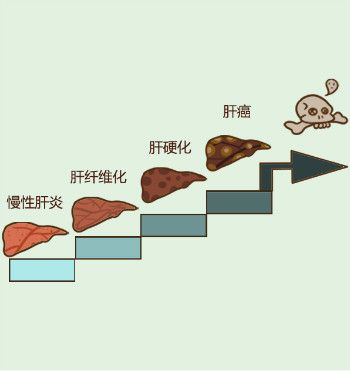

肝纤维化不能吃什么?肝纤维化饮食的注意事项有哪些?

中国人口14亿多,其中有9000万乙肝病毒感染者

-

肝硬化需要全疗程用药吗?哪个品牌的软肝片好?用药讲疗程,安全有保证!

人们常说“慢性病要以慢治慢”。古人倡导“

-

肝硬化的突出表现有哪些?用什么药软肝效果好?保肝软肝就选中成药

肝硬化是一种常见慢性病,引起肝硬化的病因

-

肝硬化的前期表现有哪些?肝硬化前期该如何选择软肝药品呢?

中国人的饮酒文化众所皆知,都特别喜欢酒桌

-

肝硬化患者吃什么药好,复方鳖甲软肝片有效吗?疗效值得认可

我国是肝病高发生率大国,每年有超过120万病

-

肝硬化吃复方鳖甲软肝片怎么样?复方鳖甲软肝片功效与作用来评价

肝硬化是一种常见的慢性肝病,是由一种或多

-

-

-

-

-

-

-

-

-

-

-

-

-

优养在线

优养在线